SLUS774B-AUGUST 2007-REVISED OCTOBER 2007

# 3-A DUAL NON-SYNCHRONOUS CONVERTER WITH INTEGRATED HIGH-SIDE MOSFET

## **FEATURES**

- 4.5-V to 28-V Input Range

- Output Voltage Range 0.8 V to 90% of Input Voltage

- Output Current Up to 3 A

- Two Fixed Switching Frequency Versions:

- TPS54383: 300 kHzTPS54386: 600 kHz

- Three Selectable Levels of Overcurrent Protection (Output 2)

- 0.8-V 1.5% Voltage Reference

- 2.1-ms Internal Soft Start

- Dual PWM Outputs 180° Out-of-Phase

- Ratiometric or Sequential Startup Modes Selectable by a Single Pin

- 85-mΩ Internal High-Side MOSFETs

- Current Mode Control

- Internal Compensation (See Page 16)

- Pulse-by-Pulse Overcurrent Protection

- Thermal Shutdown Protection at +148°C

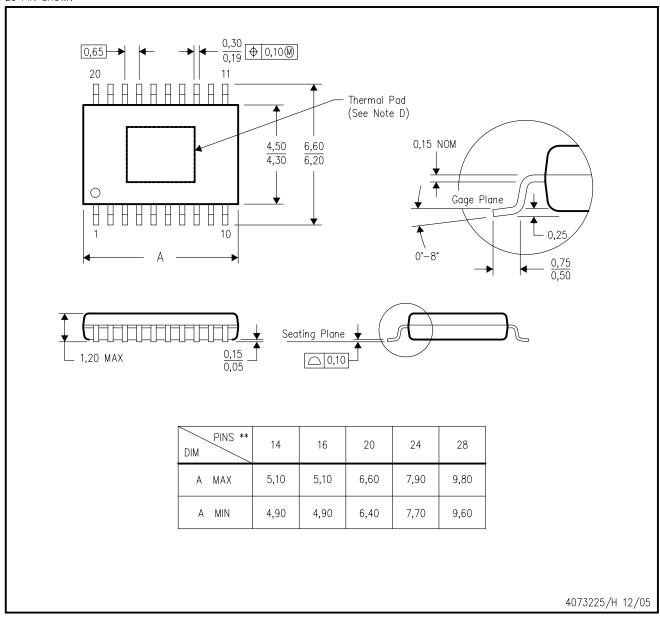

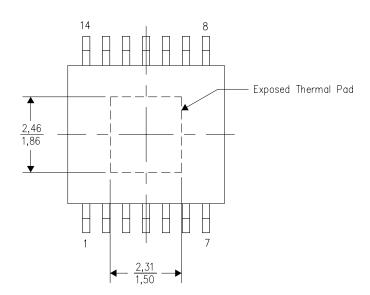

- 14-Pin PowerPAD™ HTSSOP package

## **APPLICATIONS**

- Set Top Box

- Digital TV

- Power for DSP

- Consumer Electronics

#### **CONTENTS**

| Device Ratings             | 2  |

|----------------------------|----|

| Electrical Characteristics | 3  |

| Device Information         | 9  |

| Application Information    | 12 |

| Design Examples            | 32 |

| Additional References      | 44 |

## DESCRIPTION

The TPS54383 and TPS54386 are dual output, non-synchronous buck converters capable of supporting 3-A output applications that operate from a 4.5-V to 28-V input supply voltage, and require output voltages between 0.8 V and 90% of the input voltage.

With an internally-determined operating frequency, soft start time, and control loop compensation, these converters provide many features with a minimum of external components. Channel 1 overcurrent protection is set at 4.5 A, while Channel 2 overcurrent protection level is selected by connecting a pin to ground, to BP, or left floating. The setting levels are used to allow for scaling of external components for applications that do not need the full load capability of both outputs.

The outputs may be enabled independently, or may be configured to allow either ratiometric or sequential startup sequencing. Additionally, the two outputs may be powered from different sources.

$\triangle$

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

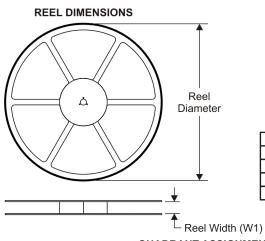

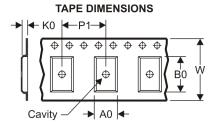

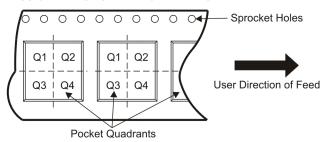

#### ORDERING INFORMATION<sup>(1)</sup>

| PART NUMBER  | OPERATING FREQUENCY (kHz) | PACKAGE                | MEDIA         | UNITS (Pieces) |

|--------------|---------------------------|------------------------|---------------|----------------|

| TPS54383PWP  | 300                       | 300                    |               | 90             |

| TPS54383PWPR | 300                       | Plastic 14-Pin HTSSOP  | Tape and Reel | 2000           |

| TPS54386PWP  | 600                       | Flastic 14-Fill H1330F | Tube          | 90             |

| TPS54386PWPR | 600                       |                        | Tape and Reel | 2000           |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### **DEVICE RATINGS**

# ABSOLUTE MAXIMUM RATINGS(1)

|                     |                             | VALUE               | UNIT |

|---------------------|-----------------------------|---------------------|------|

|                     | PVDD1, PVDD2, EN1, EN2      | 30                  |      |

|                     | BOOT1, BOOT2                | V <sub>SW</sub> + 7 |      |

|                     | SW1, SW2                    | -2 to 30            |      |

| Input voltage range | SW1, SW2 transient (< 50ns) | -3 to 31            | V    |

|                     | BP                          | 6.5                 |      |

|                     | SEQ, ILIM2                  | -0.3 to 6.5         |      |

|                     | FB1, FB2                    | -0.3 to 3           |      |

|                     | SW1, SW2 output current     | 7                   | Α    |

|                     | BP load current             | 35                  | mA   |

| T <sub>stg</sub>    | Storage temperature         | -55 to +165         |      |

| T <sub>J</sub>      | Operating temperature       | -40 to +150         | °C   |

|                     | Soldering temperature       | +260                |      |

<sup>(1)</sup> Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be limited to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to conditions beyond the operational limits for extended periods of time may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

|                |                                | MIN | MAX  | UNIT |

|----------------|--------------------------------|-----|------|------|

| $V_{PVDD2}$    | Input voltage                  | 4.5 | 28   | V    |

| T <sub>J</sub> | Operating junction temperature | -40 | +125 | °C   |

# **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

|                  | MIN  | UNIT |

|------------------|------|------|

| Human body model | 2k   |      |

| CDM              | 1.5k | V    |

| Machine Model    | 250  |      |

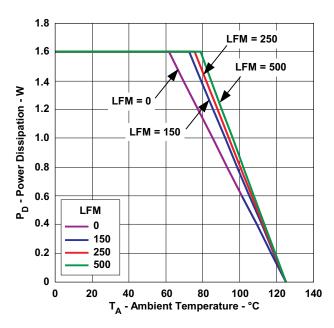

## PACKAGE DISSIPATION RATINGS(1)(2)(3)

| PACKAGE                     | THERMAL IMPEDANCE<br>JUNTION-TO-THERMAL PAD<br>(°C/W) | T <sub>A</sub> = +25°C<br>POWER RATING (W) | T <sub>A</sub> = +85°C<br>POWER RATING (W) |

|-----------------------------|-------------------------------------------------------|--------------------------------------------|--------------------------------------------|

| Plastic 14-Pin HTSSOP (PWP) | 2.07 <sup>(4)</sup>                                   | 1.6                                        | 1.0                                        |

- 1) For more information on the PWP package, refer to TI Technical Brief (SLMA002A).

- (2) TI device packages are modeled and tested for thermal performance using printed circuit board designs outlined in JEDEC standards JESD 51-3 and JESD 51-7.

- (3) For application information, see the *Power Derating* section.

- (4)  $T_{J-A} = +40^{\circ}C/W$ .

Submit Documentation Feedback

Copyright © 2007, Texas Instruments Incorporated

## **ELECTRICAL CHARACTERISTICS**

-40°C  $\leq$  T<sub>J</sub>  $\leq$  +125°C, V<sub>PVDD1</sub> = V<sub>PVDD2</sub> = 12 V, unless otherwise noted.

|                                          | PARAMETER                                           |          | TEST CONDITIONS                                                                   | MIN  | TYP  | MAX  | UNIT   |

|------------------------------------------|-----------------------------------------------------|----------|-----------------------------------------------------------------------------------|------|------|------|--------|

| INPUT SUPI                               | PLY (PVDD)                                          |          |                                                                                   |      |      |      |        |

| V <sub>PVDD1</sub>                       | Input voltage range                                 |          |                                                                                   | 4.5  |      | 28   | ٧      |

| V <sub>PVDD2</sub><br>IDD <sub>SDN</sub> | Shutdown                                            |          | $V_{EN1} = V_{EN2} = V_{PVDD2}$                                                   |      | 70   | 150  | μА     |

| IDD <sub>SDN</sub>                       |                                                     |          | $v_{EH} - v_{EN2} - v_{PVDD2}$ $V_{FB} = 0.9 \text{ V}$ , Outputs off             |      | 1.8  | 3.0  | μА     |

|                                          | Quiescent, non-switching                            |          | SW node unloaded; Measured as BP sink                                             |      |      | 3.0  | mA     |

| IDD <sub>SW</sub>                        | Quiescent, while-switching                          |          | current                                                                           |      | 5    |      |        |

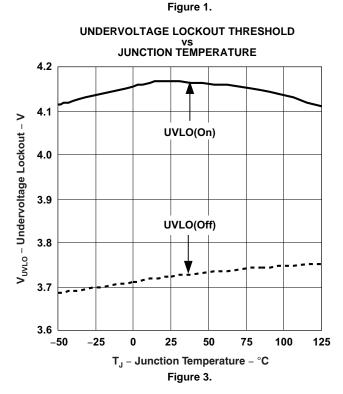

| $V_{\text{UVLO}}$                        | Minimum turn-on voltage                             |          | PVDD2 only                                                                        | 3.8  | 4.1  | 4.4  | V      |

| $V_{\text{UVLO(hys)}}$                   | Hysteresis                                          |          |                                                                                   |      | 400  |      | mV     |

| $t_{\text{START}}^{(1)(2)}$              | Time from startup to softstart begin                |          | $C_{BP} = 10 \mu F$ , $\overline{EN1}$ and $\overline{EN2}$ go low simultaneously |      | 2    |      | ms     |

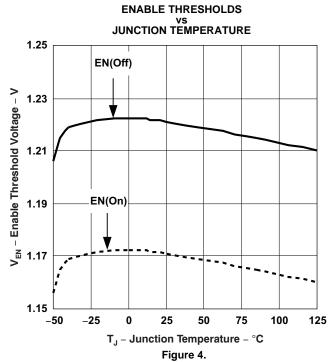

| ENABLE (E                                | N)                                                  |          |                                                                                   |      |      |      |        |

| V <sub>EN1</sub>                         | Enable threshold                                    |          |                                                                                   | 0.9  | 1.2  | 1.5  | V      |

| LIVE                                     | Hysteresis                                          |          |                                                                                   |      | 50   |      | mV     |

| l <sub>EN1</sub>                         | Enable pull-up current                              |          | $V_{\text{ENT}} = V_{\text{EN2}} = 0 \text{ V}$                                   |      | 6    | 12   | μА     |

| I <sub>EN2</sub>                         | <u> </u>                                            |          |                                                                                   |      |      |      |        |

| t <sub>EN</sub> <sup>(1)</sup>           | Time from enable to soft-start begin                |          | Other EN pin = GND                                                                |      | 10   |      | μs     |

| BP REGULA                                | • • •                                               |          |                                                                                   |      |      |      |        |

| BP                                       | Regulator voltage                                   |          | 8 V < P <sub>VDD2</sub> < 28 V                                                    | 5    | 5.25 | 5.6  | V      |

| $BP_{LDO}$                               | Dropout voltage                                     |          | $P_{VDD2}$ = 4.5 V; switching, no external load on BP                             |      | 400  |      | mV     |

| $I_{BP}^{(1)}$                           | Regulator external load                             |          |                                                                                   |      |      | 2    | mA     |

| I <sub>BPS</sub>                         | Regulator short circuit                             |          | 4.5 V < P <sub>VDD2</sub> < 28 V                                                  | 10   | 20   | 30   | 1117 ( |

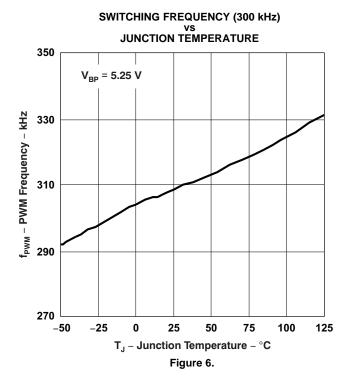

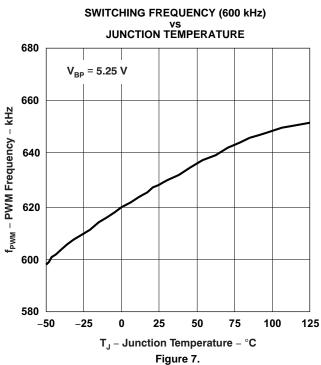

| OSCILLATO                                | DR .                                                |          |                                                                                   |      |      |      |        |

| $f_{SW}$                                 | Switching frequency                                 | TPS54383 |                                                                                   | 255  | 310  | 375  | kHz    |

|                                          |                                                     | TPS54386 |                                                                                   | 510  | 630  | 750  |        |

| t <sub>DEAD</sub> <sup>(1)</sup>         | Clock dead time                                     |          |                                                                                   |      | 140  |      | ns     |

|                                          | PLIFIER (EA) and VOLTAGE REFERENCE (RE              | F)       |                                                                                   |      |      | 1    |        |

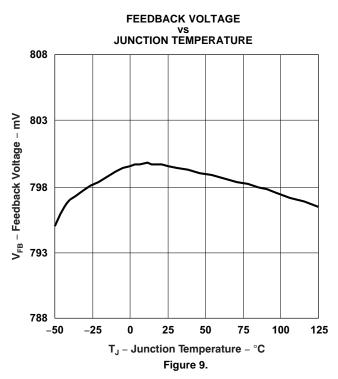

| V <sub>FB1</sub>                         | Feedback input voltage                              |          | 0°C < T <sub>J</sub> < +85°C                                                      | 788  | 800  | 812  | mV     |

| V <sub>FB2</sub>                         | ·                                                   |          | –40°C < T <sub>J</sub> < +125°C                                                   | 786  |      | 812  |        |

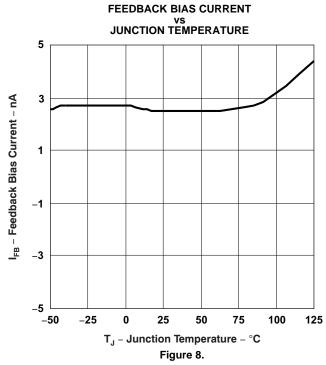

| I <sub>FB1</sub>                         | Feedback input bias current                         |          |                                                                                   |      | 3    | 50   | nA     |

| I <sub>FB2</sub>                         |                                                     |          |                                                                                   |      |      |      |        |

| g <sub>M</sub> 1 <sup>(1)</sup>          | Transconductance                                    |          |                                                                                   |      | 30   |      | μS     |

| g <sub>M</sub> 2 <sup>(1)</sup>          | NT (CC)                                             |          |                                                                                   |      |      |      |        |

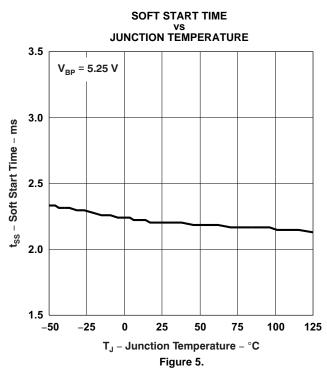

| SOFT STAR                                | (35)                                                |          |                                                                                   |      |      |      |        |

| T <sub>SS1</sub>                         | <ul> <li>Soft start time</li> </ul>                 |          |                                                                                   | 1.5  | 2.1  | 2.7  | ms     |

| T <sub>SS2</sub>                         | RENT PROTECTION                                     |          |                                                                                   |      |      |      |        |

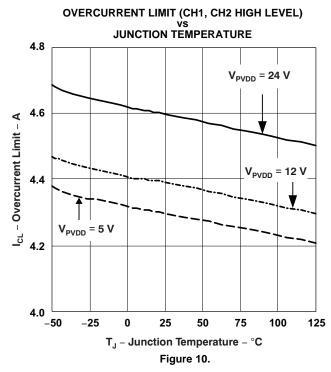

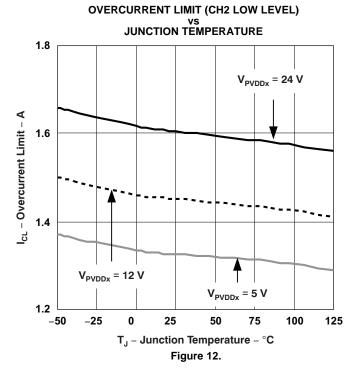

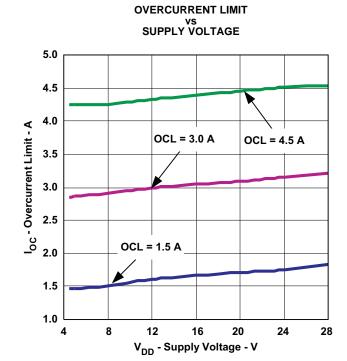

| I <sub>CL1</sub>                         | Current limit channel 1                             |          |                                                                                   | 3.6  | 4.5  | 5.6  |        |

| ·CL1                                     | $V_{ILIM2} = V_{BP}$                                |          | 3.6                                                                               | 4.5  | 5.6  |      |        |

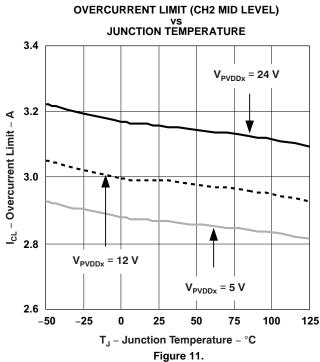

| I <sub>CL2</sub>                         | Current limit channel 2                             |          | V <sub>ILIM2</sub> = (floating)                                                   | 2.4  | 3.0  | 3.6  | Α      |

| *CL2                                     | CaSit initia Giarnoi E                              |          | V <sub>ILIM2</sub> = (IDENTIFY) V <sub>ILIM2</sub> = GND                          | 1.15 | 1.50 | 1.75 | 1      |

| V <sub>UV1</sub>                         |                                                     |          | TILINIZ TOTAL                                                                     | 1.10 | 1.00 | 1.75 |        |

| V <sub>UV2</sub>                         | Low-level output threshold to declare a fault       |          | Measured at feedback pin.                                                         |      | 670  |      | mV     |

| T <sub>HICCUP</sub> <sup>(1)</sup>       | Hiccup timeout                                      |          |                                                                                   |      | 10   |      | ms     |

| t <sub>ON1(oc)</sub> <sup>(1)</sup>      | ·                                                   |          |                                                                                   |      |      |      |        |

| t <sub>ON2(oc)</sub> <sup>(1)</sup>      | <ul> <li>Minimum overcurrent pulse width</li> </ul> |          |                                                                                   |      | 90   | 150  | ns     |

<sup>(1)</sup> Ensured by design. Not production tested.

When both outputs are started simultaneously, a 20-mA current source charges the BP capacitor. Faster times are possible with a lower BP capacitor value. More information can be found in the *Input UVLO and Startup* section.

# **ELECTRICAL CHARACTERISTICS (continued)**

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le +125^{\circ}\text{C}$ ,  $\text{V}_{\text{PVDD1}} = \text{V}_{\text{PVDD2}} = 12 \text{ V}$ , unless otherwise noted.

|                                                                        | PARAMETER                                  | TEST CONDITIONS | MIN                                                       | TYP | MAX | UNIT |       |

|------------------------------------------------------------------------|--------------------------------------------|-----------------|-----------------------------------------------------------|-----|-----|------|-------|

| BOOTSTRA                                                               | P                                          |                 |                                                           |     |     |      |       |

| R <sub>BOOT2</sub>                                                     | - Bootstrap switch resistance              |                 | From BP to BOOT1 or BP to BOOT2, I <sub>EXT</sub> = 50 mA |     | 18  |      | Ω     |

| OUTPUT ST                                                              | OUTPUT STAGE (Channel 1 and Channel 2)     |                 |                                                           |     |     |      |       |

| R <sub>DS(on)</sub> <sup>(3)</sup>                                     | MOSEET on registence plus band wire regist | anaa            | $T_J = +25$ °C, $V_{PVDD2} = 8 \text{ V}$                 |     | 85  |      | mΩ    |

| R <sub>DS(on)</sub> (3) MOSFET on resistance plus bond wire resistance |                                            | ance            | -40°C < T <sub>J</sub> < +125°C, V <sub>PVDD2</sub> = 8 V |     | 85  | 165  | 11122 |

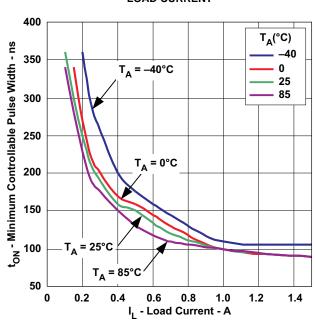

| t <sub>ON(min)</sub> (3)                                               | Minimum controllable pulse width           |                 | I <sub>SWx</sub> peak current > 1 A <sup>(4)</sup>        |     | 100 | 200  | ns    |

| D <sub>MIN</sub>                                                       | Minimum Duty Cycle                         |                 | V <sub>FB</sub> = 0.9 V                                   |     |     | 0    | %     |

| <b>D</b>                                                               | Maximum Duty Cycle                         | TPS54383        | f <sub>SW</sub> = 300 kHz                                 | 90  | 95  |      | %     |

| D <sub>MAX</sub>                                                       | Maximum Duty Cycle                         | TPS54386        | f <sub>SW</sub> = 600 kHz                                 | 85  | 90  |      | %     |

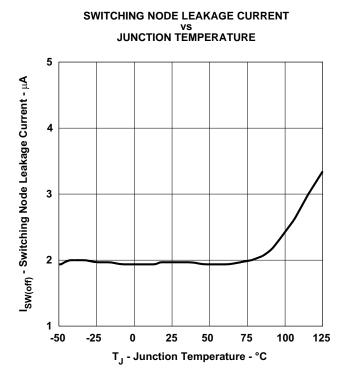

| I <sub>SW</sub>                                                        | Switching node leakage current (sourcing)  | Outputs OFF     |                                                           | 2   | 12  | μΑ   |       |

| THERMAL S                                                              | HUTDOWN                                    |                 |                                                           |     |     |      |       |

| T <sub>SD</sub> <sup>(3)</sup>                                         | Shutdown temperature                       |                 |                                                           |     | 148 |      | °C    |

| T <sub>SD(hys)</sub> <sup>(3)</sup>                                    | Hysteresis                                 |                 |                                                           |     | 20  |      | C     |

<sup>(3)</sup> Ensured by design. Not production tested.

(4) See Figure 14 for I<sub>SWx</sub> peak current <1 A.</li>

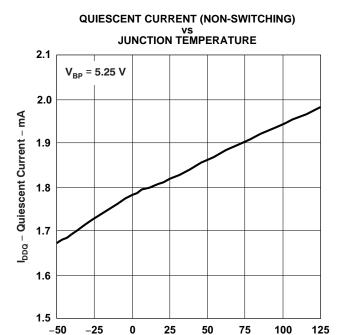

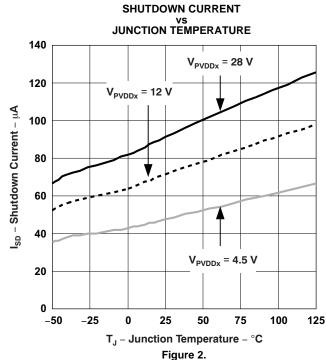

## TYPICAL CHARACTERISTICS

T<sub>J</sub> – Junction Temperature – °C

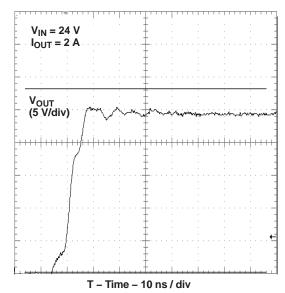

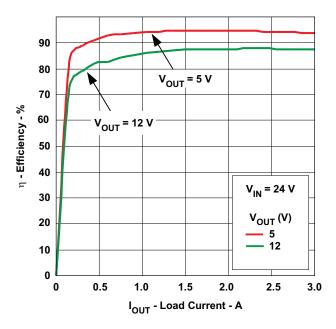

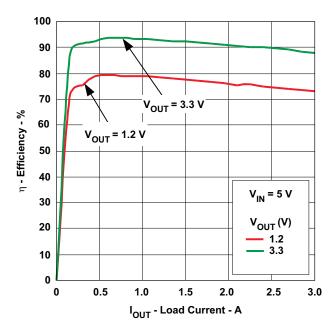

# **TYPICAL CHARACTERISTICS (continued)**

# **TYPICAL CHARACTERISTICS (continued)**

# **TYPICAL CHARACTERISTICS (continued)**

# MINUMUM CONTROLLABLE PULSE WIDTH vs LOAD CURRENT

Figure 13.

Figure 14.

Figure 15.

## **DEVICE INFORMATION**

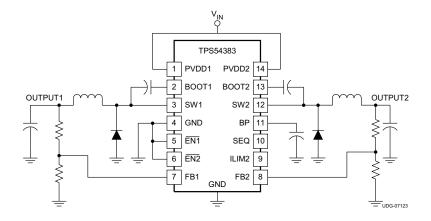

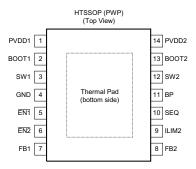

# **PIN CONNECTIONS**

## **TERMINAL FUNCTIONS**

| TERM  | IINAL |     | DECODINE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO.   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BOOT1 | 2     | I   | Input supply to the high side gate driver for Output 1. Connect a 22-nF to 82-nF capacitor from this pin to SW1. This capacitor is charged from the BP pin voltage through an internal switch. The switch is turned ON during the OFF time of the converter. To slow down the turn ON of the internal FET, a small resistor (1 $\Omega$ to 3 $\Omega$ ) may be placed in series with the bootstrap capacitor.                                                                                                             |

| BOOT2 | 13    | I   | Input supply to the high side gate driver for Output 2. Connect a 22-nF to 82-nF capacitor from this pin to SW2. This capacitor is charged from the BP pin voltage through an internal switch. The switch is turned ON during the OFF time of the converter. To slow down the turn ON of the internal FET, a small resistor (1 $\Omega$ to 3 $\Omega$ ) may be placed in series with the bootstrap capacitor.                                                                                                             |

| BP    | 11    | -   | Regulated voltage to charge the bootstrap capacitors. Bypass this pin to GND with a low ESR (4.7- $\mu$ F to 10- $\mu$ F X7R or X5R) ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                   |

| EN1   | 5     | I   | Active low enable input for Output 1. If the voltage on this pin is greater than 1.55 V, Output 1 is disabled (high-side switch is OFF). A voltage of less than 0.9 V enables Output 1 and allows soft start of Output 1 to begin. An internal current source drives this pin to PVDD2 if left floating. Connect this pin to GND for "always ON" operation.                                                                                                                                                               |

| EN2   | 6     | I   | Active low enable input for Output 2. If the voltage on this pin is greater than 1.55 V, Output 2 is disabled (high-side switch is OFF). A voltage of less than 0.9 V enables Output 2 and allows soft start of Output 2 to begin. An internal current source drives this pin to PVDD2 if left floating. Connect this pin to GND for "always ON" operation.                                                                                                                                                               |

| FB1   | 7     | ı   | Voltage feedback pin for Output 1. The internal transconductance error amplifier adjusts the PWM for Output 1 to regulate the voltage at this pin to the internal 0.8-V reference. A series resistor divider from Output 1 to ground, with the center connection tied to this pin, determines the value of the regulated output voltage. Compensation for the feedback loop is provided internally to the device. See Feedback Loop and Inductor-Capacitor (L-C) Filter Selection section for further information.        |

| FB2   | 8     | ı   | Voltage feedback pin for Output 2. The internal transconductance error amplifier adjusts the PWM for Output 2 to regulate the voltage at this pin to the internal 0.8-V reference. A series resistor divider from Output 2 to ground, with the center connection tied to this pin, determines the value of the regulated Output voltage. Compensation for the feedback loop is provided internally to the device. See Feedback Loop and Inductor-Capacitor (L-C) Filter Selection section for further information.        |

| GND   | 4     | -   | Ground pin for the device. Connect directly to Thermal Pad.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ILIM2 | 9     | I   | Current limit adjust pin for Output 2 only. This function is intended to allow a user with asymmetrical load currents (Output 1 load current much greater than Output 2 load current) to optimize component scaling of the lower current output while maintaining proper component derating in a overcurrent fault condition. The discrete levels are available as shown in Table 2, Current Limit Threshold Adjustment for Output 2. Note: An internal 2-resistor divider (150-kΩ each) connects BP to ILIM2 and to GND. |

| PVDD1 | 1     | I   | Power input to the Output 1 high side MOSFET only. This pin should be locally bypassed to GND with a low ESR ceramic capacitor of $10$ - $\mu$ F or greater.                                                                                                                                                                                                                                                                                                                                                              |

| PVDD2 | 14    | I   | The PVDD2 pin provides power to the device control circuitry, provides the pull-up for the EN1 and EN2 pins and provides power to the Output 2 high-side MOSFET. This pin should be locally bypassed to GND with a low ESR ceramic capacitor of 10-μF or greater. The UVLO function monitors PVDD2 and enables the device when PVDD2 is greater than 4.1 V.                                                                                                                                                               |

# **TERMINAL FUNCTIONS (continued)**

| TERMINAL    |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |     |     | This pin configures the output startup mode. If the SEQ pin is connected to BP, then when Output 2 is enabled, Output 1 is allowed to start after Output 2 has reached regulation; that is, sequential startup where Output 1 is slave to Output 2. If $\overline{\text{EN2}}$ is allowed to go high after the outputs have been operating, then both outputs are disabled immediately, and the output voltages decay according to the load that is present. For this sequence configuration, tie $\overline{\text{EN1}}$ to ground. |

| SEQ 10 I    |     | I   | If the SEQ pin is connected to GND, then when Output 1 is enabled, Output 2 is allowed to start after Output 1 has reached regulation; that is, sequential startup where Output 2 is slave to Output 1. If $\overline{\text{EN1}}$ is allowed to go high after the outputs have been operating, then both outputs are disabled immediately, and the output voltages decay according to the load that is present. For this sequence configuration, tie $\overline{\text{EN2}}$ to ground.                                             |

|             |     |     | If left floating, Output 1 and Output 2 start ratio-metrically when both outputs are enabled at the same time. They will soft start at a rate determined by their final output voltage and enter regulation at the same time. If the EN1 and EN2 pins are allowed to operate independently, then the two outputs also operate independently NOTE: An internal two resistor (150-kΩ each) divider connects BP to SEQ and to GND. See the Sequence States table.                                                                       |

| SW1         | 3   | 0   | Source (switching) output for Output 1 PWM. A snubber is recommended to reduce ringing on this node. See SW Node Ringing for further information.                                                                                                                                                                                                                                                                                                                                                                                    |

| SW2         | 12  | 0   | Source (switching) output for Output 2 PWM. A snubber is recommended to reduce ringing on this node. See SW Node Ringing for further information.                                                                                                                                                                                                                                                                                                                                                                                    |

| Thermal Pad | -   | -   | This pad must be tied externally to a ground plane and the GND pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

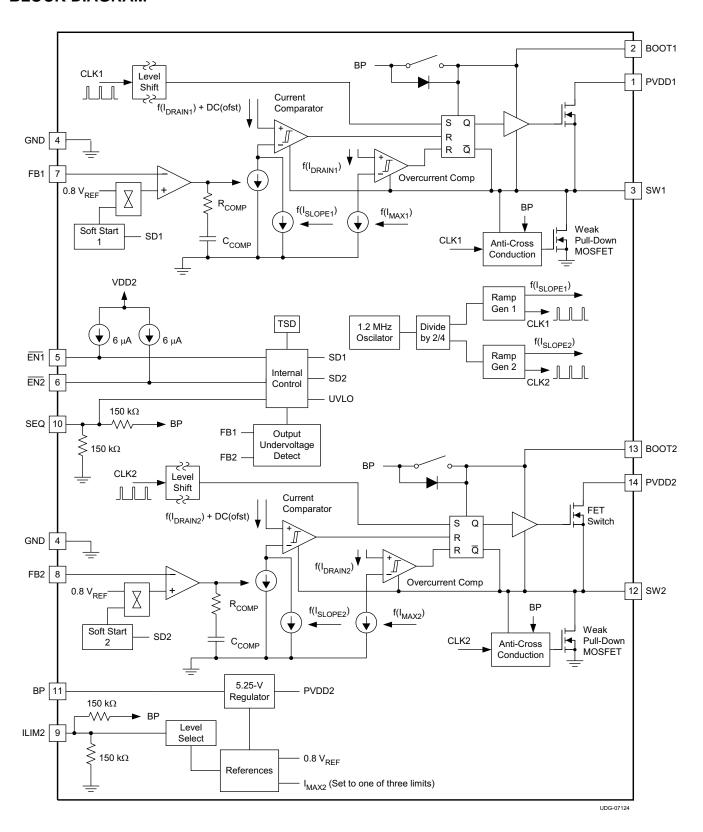

## **BLOCK DIAGRAM**

#### APPLICATION INFORMATION

#### **FUNCTIONAL DESCRIPTION**

The TPS54383 and TPS54386 are dual output, non-synchronous converters. Each PWM channel contains an internally-compensated error amplifier, current mode pulse width modulator (PWM), switch MOSFET, enable, and fault protection circuitry. Common to the two channels are the internal voltage regulator, voltage reference, clock oscillator, and output voltage sequencing functions.

#### **DESIGN HINT**

The TPS5438x contains internal slope compensation and loop compensation components; therefore, the external L-C filter must be selected appropriately so that the resulting control loop meets criteria for stability. This approach differs from an externally-compensated controller, where the L-C filter is generally selected first, and the compensation network is found afterwards. (See Feedback Loop and L-C Filter Selection section.)

#### NOTE:

Unless otherwise noted, the term TPS5438x applies to both the TPS54383 and TPS54386. Also, unless otherwise noted, a label with a lowercase x appended implies the term applies to both outputs of the two modulator channels. For example, the term  $\overline{ENx}$  implies both  $\overline{EN1}$  and  $\overline{EN2}$ . Unless otherwise noted, all parametric values given are typical. Refer to the *Electrical Characteristics* for minimum and maximum values. Calculations should be performed with tolerance values taken into consideration.

#### **Voltage Reference**

The bandgap cell common to both outputs, trimmed to 800 mV.

## Oscillator

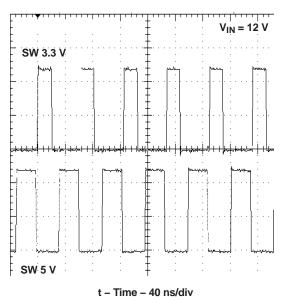

The oscillator frequency is internally fixed at two times the SWx node switching frequency. The two outputs are internally configured to operate on alternating switch cycles (that is, 180° out of phase).

## Input Undervoltage Lockout (UVLO) and Startup

When the voltage at the PVDD2 pin is less than 4.1 V, a portion of the internal bias circuitry is operational, and all other functions are held OFF. All of the internal MOSFETs are also held OFF. When the PVDD2 voltage rises above the UVLO turn-on threshold, the state of the enable pins determines the remainder of the internal startup sequence. If either output is enabled (ENx pulled low), the BP regulator turns on, charging the BP capacitor with a 20-mA current. When the BP pin is greater than 4 V, PWM is enabled and soft start begins, depending on the SEQ mode of operation and the  $\overline{\text{EN1}}$  and  $\overline{\text{EN2}}$  settings.

Note that the internal regulator and control circuitry are powered from PVDD2. The voltage on PVDD1 may be higher or lower than PVDD2. (See the *Dual Supply Operation* section.)

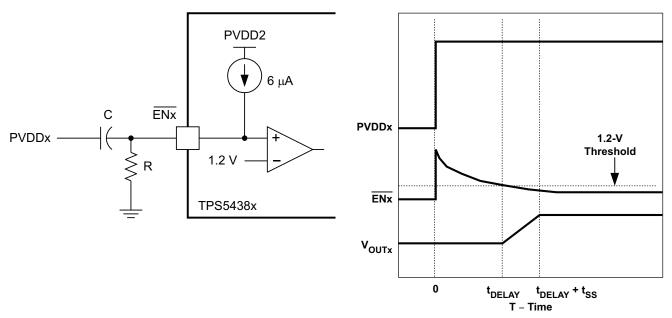

## **Enable and Timed Turn On of the Outputs**

Each output has a dedicated (active low) enable pin. If left floating, an internal current source pulls the pin to PVDD2. By grounding, or by pulling the ENx pin to below approximately 1.2 V with an external circuit, the associated output is enabled and soft start is initiated.

If both enable pins are left in the high state, the device operates in a shutdown mode, where the BP regulator is shut down and minimal functions are active. The total standby current from both PVDD pins is approximately 70 μA at 12-V input supply.

An R-C connected to an  $\overline{ENx}$  pin may be used to delay the turn-on of the associated output after power is applied to PVDDx (see Figure 16). After power is applied to PVDD2, the voltage on the  $\overline{ENx}$  pin slowly decays towards ground. Once the voltage decays to approximately 1.2 V, then the output is enabled and the startup sequence begins. If it is desired to enable the outputs of the device immediately upon the application of power to PVDD2, then omit these two components and tie the  $\overline{ENx}$  pin to GND directly.

If an R-C circuit is used to delay the turn-on of the output, the resistor value must be much less than 1.2 V /  $6\mu A$  or 200 k $\Omega$ . A suggested value is 51 k $\Omega$ . This resistor value allows the  $\overline{ENx}$  voltage to decay below the 1.2-V threshold while the  $6-\mu A$  bias current flows.

The capacitor value required to delay the startup time (after the application of PVDD2) is shown in Equation 1.

$$C = \frac{t_{DELAY}}{R \times \ell n \left(\frac{V_{IN} - 2 \times I_{ENx} \times R}{V_{TH} - I_{ENx} \times R}\right)} farads \tag{1}$$

where:

- R and C are the timing components

- V<sub>TH</sub> is the 1.2-V enable threshold voltage

- I<sub>ENx</sub> is the 6 μA enable pin biasing current

Other enable pin functionality is dictated by the state of the SEQ pin. (See the *Output Voltage Sequencing* section.)

Figure 16. Startup Delay Schematic

Figure 17. Startup Delay with R-C on Enable

#### **DESIGN HINT**

If delayed output voltage startup is not necessary, simply connect  $\overline{\text{EN1}}$  and  $\overline{\text{EN2}}$  to GND. This configuration allows the outputs to start immediately on valid application of PVDD2.

If  $\overline{\text{ENx}}$  is allowed to go *high* after the Outputx has been in regulation, the upper MOSFET shuts off, and the output decays at a rate determined by the output capacitor and the load. The internal pulldown MOSFET remains in the OFF state. (See the *Bootstrap for N-Channel MOSFET* section.)

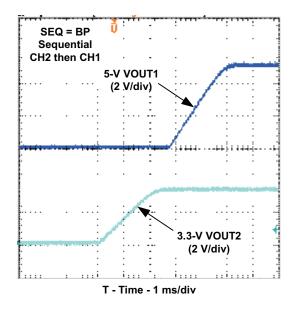

#### **Output Voltage Sequencing**

The TPS5438x allows single-pin programming of output voltage startup sequencing. During power-on, the state of the SEQ pin is detected. Based on whether the pin is tied to BP, to GND, or left floating, the outputs behave as described in Table 1.

**Table 1. Sequence States**

| SEQ PIN STATE | MODE                                              | EN1                                                                                                                                                           | EN2                                                                                                                                                           |

|---------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                                                   | Ignored by the device.when V <sub>EN2</sub> < enable threshold voltage                                                                                        |                                                                                                                                                               |

| BP            | Sequential, Output 2 then Output 1                | Tie EN1 to < enable threshold voltage for BP to be active when V <sub>EN2</sub> > enable threshold voltage                                                    | Active                                                                                                                                                        |

|               |                                                   | Tie $\overline{\text{EN1}}$ to > enable threshold voltage for low quiescent current (BP inactive) when $V_{\overline{\text{EN2}}}$ > enable threshold voltage |                                                                                                                                                               |

|               |                                                   | I then Output 2 Active                                                                                                                                        | Ignored by the device.when V <sub>EN1</sub> < enable threshold voltage                                                                                        |

| GND           | Sequential, Output 1 then Output 2                |                                                                                                                                                               | Tie EN2 to < enable threshold voltage for BP to be active when V <sub>EN1</sub> > enable threshold voltage                                                    |

|               |                                                   |                                                                                                                                                               | Tie $\overline{\text{EN2}}$ to > enable threshold voltage for low quiescent current (BP inactive) when $V_{\overline{\text{ENT}}}$ > enable threshold voltage |

| (floating)    | Independent or Ratiometric, Output 1 and Output 2 | Active. EN1 and EN2 must be tied together for Ratio-metric startup.                                                                                           | Active. EN1 and EN2 must be tied together for Ratio-metric startup.                                                                                           |

If the SEQ pin is connected to BP, then when Output 2 is enabled, Output 1 is allowed to start approximately 400 µs after Output 2 has reached regulation; that is, sequential startup where Output 1 is slave to Output 2. If EN2 is allowed to go high after the outputs have been operating, then both outputs are disabled immediately, and the output voltages decay according to the load that is present.

If the SEQ pin is connected to GND, then when Output 1 is enabled, Output 2 is allowed to start approximately 400 µs after Output 1 has reached regulation; that is, sequential startup where Output 2 is slave to Output 1. If EN1 is allowed to go high after the outputs have been operating, then both outputs are disabled immediately, and the output voltages decay according to the load that is present.

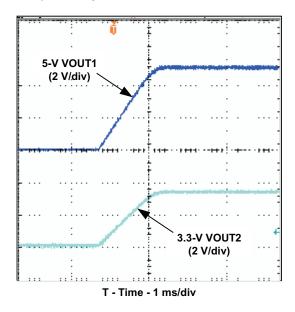

Figure 18. SEQ Pin Tled to BP

Figure 19. SEQ Pin Tied to GND

#### NOTE:

An R-C network connected to the  $\overline{\text{ENx}}$  pin may be used in addition to the SEQ pin in sequential mode to delay the startup of the first output voltage. This approach may be necessary in systems with a large number of output voltages and elaborate voltage sequencing requirements. See *Enable and Timed Turn On of the Outputs*.

If the SEQ pin is left floating, Output 1 and Output 2 each start ratiometrically when both outputs are enabled at the same time. Output 1 and Output 2 soft start at a rate that is determined by the respective final output voltages and enter regulation at the same time. If the  $\overline{\text{EN1}}$  and  $\overline{\text{EN2}}$  pins are allowed to operate independently, then the two outputs also operate independently.

Figure 20. SEQ Pin Floating

#### **Soft Start**

Each output has a dedicated soft start circuit. The soft start voltage is an internal digital reference ramp to one of two noninverting inputs of the error amplifier. The other input is the (internal) precision 0.8-V reference. The total ramp time for the FB voltage to charge from 0 V to 0.8 V is about 2.1 ms. During a soft start interval, the TPS5438x output slowly increases the voltage to the noninverting input of the error amplifier. In this way, the output voltage ramps up slowly until the voltage on the noninverting input to the error amplifier reaches the internal 0.8 V reference voltage. At that time, the voltage at the noninverting input to the error amplifier remains at the reference voltage.

#### NOTE:

To avoid a disturbance in the output voltage during the stepping of the digital soft start, a minimum output capacitance of  $50\mu F$  is recommended. See *Feedback Loop and Inductor-Capacitor (L-C) Filter Selection* Once the filter and compensation components have been established, laboratory measurements of the physical design should be performed to confirm converter stability.

During the soft start interval, pulse-by-pulse current limiting is in effect. If an overcurrent pulse is detected, six PWM pulses are skipped to allow the inductor current to decay before another PWM pulse is applied. (See the *Output Overload Protection* section.) There is no pulse skipping if a current limit pulse is not detected.

#### **DESIGN HINT**

If the rate of rise of the input voltage (PVDDx) is such that the input voltage is too low

to support the desired regulation voltage by the time Soft Start has completed, then the output UV circuit may trip and cause a *hiccup* in the output voltage. In this case, use a timed delay startup from the  $\overline{\text{ENx}}$  pin to delay the startup of the output until the PVDDx voltage has the capability of supporting the desired regulation voltage. See *Operating Near Maximum Duty Cycle* and *Maximum Output Capacitance* for related information.

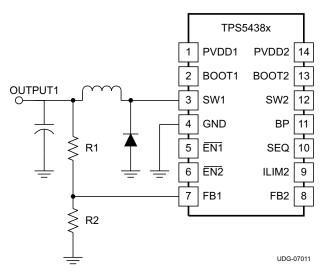

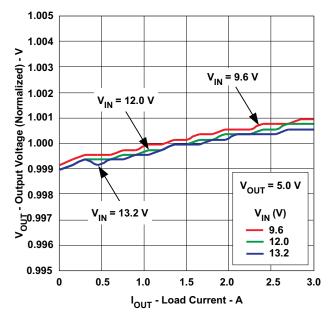

#### **Output Voltage Regulation**

Each output has a dedicated feedback loop comprised of a voltage setting divider, an error amplifier, a pulse width modulator, and a switching MOSFET. The regulation output voltage is determined by a resistor divider connecting the output node, the FBx pin, and GND (see Figure 21). Assuming the value of the upper voltage setting divider is known, the value of the lower divider resistor for a desired output voltage is calculated by Equation 2.

$$R2 = R1 \times \left( \frac{V_{REF}}{V_{OUT} - V_{REF}} \right)$$

(2)

where

V<sub>REF</sub> is the internal 0.8-V reference voltage

Figure 21. Feedback Network for Channel 1

## **DESIGN HINT**

There is a leakage current of up to 12  $\mu A$  out of the SW pin when a single output of the TPS5438x is disabled. Keeping the series impedance of R1 + R2 less than 50 k $\Omega$  prevents the output from floating above the referece voltage while the controller output is in the OFF state.

# Feedback Loop and Inductor-Capacitor (L-C) Filter Selection

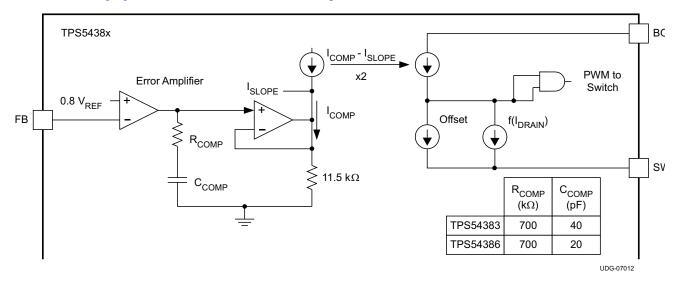

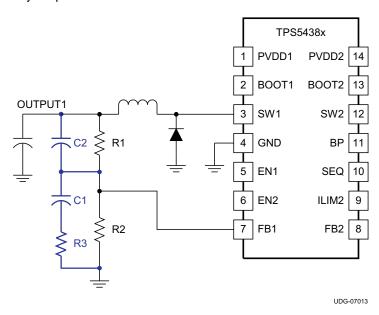

In the feedback signal path, the output voltage setting divider is followed by an internal  $g_M$ -type error amplifier with a typical transconductance of 30  $\mu$ S. An internal series connected R-C circuit from the  $g_M$  amplifier output to ground serves as the compensation network for the converter. The signal from the error amplifier output is then buffered and combined with a slope compensation signal before it is mirrored to be referenced to the SW node. Here, it is compared with the current feedback signal to create a pulse-width-modulated (PWM) signal-fed to drive the upper MOSFET switch. A simplified equivalent circuit of the signal control path is depicted in Figure 22.

#### NOTE:

Noise coupling from the SWx node to internal circuitry of BOOTx may impact narrow pulse width operation, especially at load currents less than 1 A. See SW Node Ringing for further information on reducing noise on the SWx node.

Figure 22. Feedback Loop Equivalent Circuit

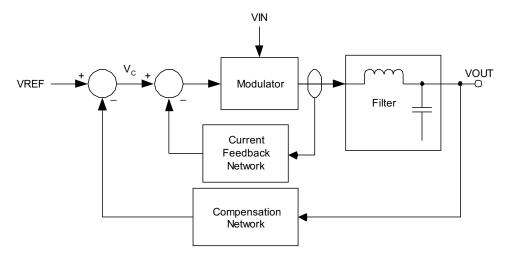

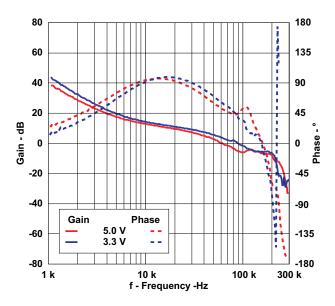

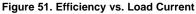

A more conventional small signal equivalent block diagram is shown in Figure 23. Here, the full closed loop signal path is shown. Because the TPS5438x contains internal slope compensation and loop compensation components, the external L-C filter must be selected appropriately so that the resulting control loop meets criteria for stability. This approach differs from an externally-compensated controller, where the L-C filter is generally selected first, and the compensation network is found afterwards. To find the appropriate L and C filter combination, the Output-to-Vc signal path plots (see the next section) of gain and phase are used along with other design criterial to aid in finding the combinations that best results in a stable feedback loop.

Figure 23. Small Signal Equivalent Block Diagram

# Inductor-Capacitor (L-C) Selection

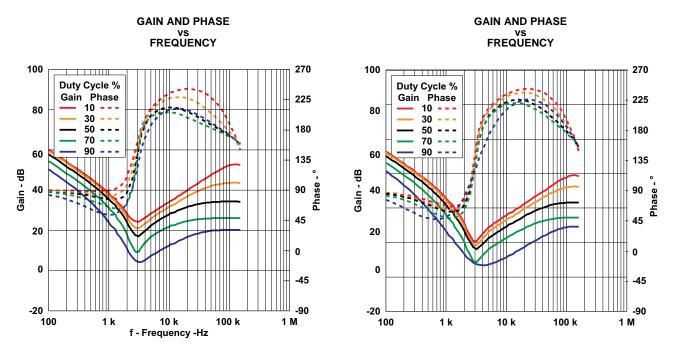

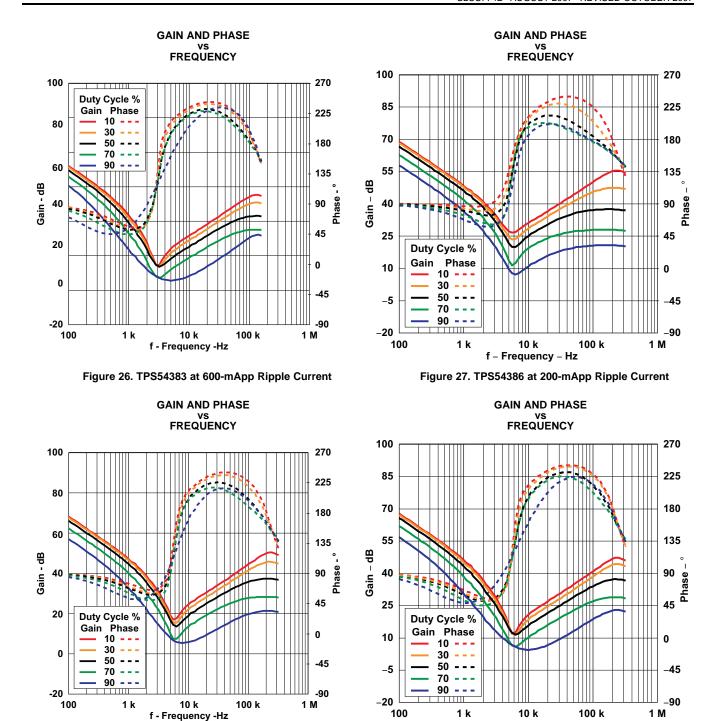

The following figures plot the TPS5438x Output-to-Vc gain and phase versus frequency for various duty cycles (10%, 30%, 50%, 70%, 90%) at three (200 mA, 400 mA, 600 mA) peak-to-peak ripple current levels. The loop response curve selected to compensate the loop is based on the duty cycle of the application and the ripple current in the inductor. Once the curve has been selected and the inductor value has been calculated, the output capacitor is found by calculating the L-C resonant frequency required to compensate the feedback loop. A brief example follows the curves.

Note that the internal error amplifier compensation is optimized for output capacitors with an ESR zero frequency between 20 kHz and 60 kHz. See the following sections for further details.

Figure 24. TPS54383 at 200-mApp Ripple Current

Figure 25. TPS54383 at 400-mApp Ripple Current

Figure 28. TPS54386 at 400-mApp Ripple Current

Figure 29. TPS54386 at 600-mApp Ripple Current

f - Frequency - Hz

## **Maximum Output Capacitance**

With internal pulse-by-pulse current limiting and a fixed soft start time, there is a maximum output capacitance which may be used before startup problems begin to occur. If the output capacitance is large enough so that the device enters a current limit protection mode during startup, then there is a possibility that the output will never reach regulation. Instead, the TPS5438x simply shuts down and attempts a restart as if the output were short-circuited to ground. The maximum output capacitance (including bypass capacitance distributed at the load) is given by Equation 3:

$$C_{OUTmax} = \frac{t_{SS}}{V_{REF}} \left[ I_{CLx} - V_{REF} (1 + \frac{R1}{R2}) (1 - \frac{V_{REF} (1 + \frac{R1}{R2}) \times T_{S}}{2 \times V_{IN} \times L} + \frac{1}{R_{LOAD}}) \right]$$

(3)

## **Minimum Output Capacitance**

Ensure the value of capacitance selected for closed loop stability is compatible with the requirements of *Soft Start*.

## **Modifying The Feedback Loop**

Within the limits of the internal compensation, there is flexibility in the selection of the inductor and output capacitor values. A smaller inductor increases ripple current, and raises the resonant frequency, thereby incerasing the required amount of output capacitance. A smaller capacitor could also be used, increasing the resonant frequency, and increasing the overall loop bandwidth—perhaps at the expense of adequate phase margin.

The internal compensation of the TPS54x8x is designed for capacitors with an ESR zero frequency between 20kHz and 60kHz. It is possible, with additional feedback compensation components, to use capacitors with higher or lower ESR zero frequencies. For either case, the components C1 and R3 (ref.Figure 30) are added to re-compensate the feedback loop for stability. In this configuration a low frequency pole is followed by a higher frequency zero. The placement of this pole-zero pair is dependent on the type of output capacitor used, and the desired closed loop frequency response.

Figure 30. Optional Loop Compensation Components

#### NOTE:

Once the filter and compensation components have been established, laboratory measurements of the physical design should be performed to confirm converter stability.

#### Using High-ESR Output Capacitors

If a high ESR capacitor is used in the output filter, a zero appears in the loop response that could lead to instability. To compensate, a small R-C series connected network is placed in parallel with the lower voltage setting divider resistor (Ref Figure 30). The values of the components are determined such that a pole is placed at the same frequency as the ESR zero and a new zero is placed at a frequency location conducive to good loop stability.

The value of the resistor is calculated using a ratio of impedances to match the ratio of ESR zero frequency to the desired zero frequency.

$$R3 = \frac{R2}{\left(\left(\frac{f_{ZERO(desired)}}{f_{ESR(zero)}}\right) - 1\right)}$$

(4)

#### where:

- $f_{\rm ESR(zero)}$  is the ESR zero frequency of the output capacitor.

- f<sub>ZERO(desired)</sub> is the desired frequency of the zero added to the feedback. This frequency should be placed between 20 kHz and 60 kHz to ensure good loop stability.

Copyright © 2007, Texas Instruments Incorporated

The value of the capacitor is calculated in Equation 5.

$$C1 = \frac{1}{2\pi \times R_{EQ} \times f_{ESR(zero)}}$$

(5)

where:

R<sub>EQ</sub> is an equivalent impedance created by the parallel combination of the voltage setting divider resistors (R1 and R2) in series with R3.

$$R_{EQ} = R3 + \frac{1}{\left(\left(\frac{1}{R1}\right) + \left(\frac{1}{R2}\right)\right)}$$

(6)

#### Using All Ceramic Output Capacitors

With low ESR ceramic capacitors, there may not be enough phase margin at the crossover frequency. In this case, (Ref Figure 30) resistor R3 is set equal to 1/2 R2. This lowers the gain by 6 dB, reduce the crossover frequency, and improve phase margin.

The value of C1 is found by determining the frequency to place the low frequency pole. The minimum frequency to place the pole is 1 kHz. Any lower, and the time constant will be too slow and interfere with the internal soft start. (Ref. Soft Start) The upper bound for the pole frequency is determined by the operating frequency of the converter. It is 3 kHz for the TPS54x83, and 6 kHz for the TPS54x86. C1 is then found from Equation 7. Keep component tolerances in mind when selecting the desired pole frequency.

$$C1 = \frac{1}{2\pi \times R_{EQ} \times f_{POLE(desired)}}$$

(7)

where:

- f<sub>POLE(desired)</sub> is the desired pole frequency between 1 kHz and 3 kHz (TPS54x83) or 1 kHz and 6 kHz (TPS54x86).

- R<sub>EQ</sub> is an equivalent impedance created by the parallel combination of the voltage setting divider resistors (R1 and R2) in series with R3.

$$R_{EQ} = R3 + \frac{1}{\left(\left(\frac{1}{R1}\right) + \left(\frac{1}{R2}\right)\right)}$$

(8)

If it is necessary to increase phase margin, place a capacitor in parallel with the upper voltage setting divider resistor (Ref. C2 in Equation 9).

$$C2 = \frac{1}{2\pi \times f_{C} \times R1} \times \sqrt{1 + \frac{R1}{\left(\frac{(R2 \times R3)}{(R2 + R3)}\right)}}$$

(9)

where

f<sub>C</sub> is the unity gain crossover frequency, (approximately 50 kHz for most designs following these guidelines)

22 Submit De

# Example: TPS54386 Buck Converter Operating at 12-V Input, 3.3-V Output and 400-mA<sub>(P-P)</sub> Ripple Current

First, the steady state duty cycle is calculated. Assuming the rectifier diode has a voltage drop of 0.5 V, the duty cycle is approximated using Equation 10.

$$\delta = \frac{V_{\text{OUT}} + V_{\text{DIODE}}}{V_{\text{IN}} + V_{\text{DIODE}}} = \frac{3.3 + 0.5}{12 + 0.5} = 30\%$$

(10)

The filter inductor is then calculated; see Equation 11.

$$L = \frac{V_{IN} - V_{OUT}}{\Delta I_L} \times \delta \times T_S = \frac{12 - 3.3}{0.4} \times 0.3 \times \frac{1}{600000} = 10.9 \,\mu\text{H} \tag{11}$$

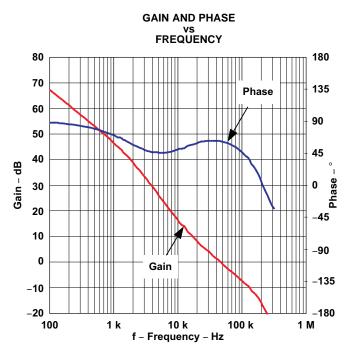

A custom-designed inductor may be used for the application, or a standard value close to the calculated value may be used. For this example, a standard  $10-\mu H$  inductor is used. Using Figure 28, find the 30% duty cycle curve. The 30% duty cycle curve has a down slope from low frequency and rises at approximately 6 kHz. This curve is the resonant frequency that must be compensated. Any frequency wthin an octave of the peak may be used in calculating the capacitor value. In this example, 6 kHz is used.

$$C = \frac{1}{L \times (2 \times \pi \times f_{RES})^2} = \frac{1}{10 \times 10^{-6} \times (2 \times 3.14 \times 6000)^2} = 70 \,\mu\text{F}$$

(12)

A 68- $\mu$ F capacitor should be used as a bulk capacitor, with up to 10  $\mu$ F of ceramic bypass capacitance. To ensure the ESR zero does not significantly impact the loop response, the ESR of the bulk capacitor should be placed a decade above the resonant frequency.

$$R_{ESR} < \frac{1}{2 \times \pi \times 10 \times f_{RES} \times C} = \frac{1}{2 \times 3.14 \times 10 \times 6000 \times 68 \times (10)^{-6}} \approx 40 \text{ m}\Omega$$

(13)

The resulting loop gain and phase are shown in Figure 31. Based on measurement, loop crossover is 45 kHz with a phase margin of 60 degrees.

Figure 31. Example Loop Result

### **Bootstrap for the N-Channel MOSFET**

A bootstrap circuit provides a voltage source higher than the input voltage and of sufficient energy to fully enhance the switching MOSFET each switching cycle. The PWM duty cycle is limited to a maximum of 90%, allowing an external bootstrap capacitor to charge through an internal synchronous switch (between BP and BOOTx) during every cycle. When the PWM switch is commanded to turn ON, the energy used to drive the MOSFET gate is derived from the voltage on this capacitor.

To allow the bootstrap capacitor to charge each switching cycle, an internal pulldown MOSFET (from SW to GND) is turned ON for approximately 140 ns at the beginning of each switching cycle. In this way, if, during light load operation, there is insufficient energy for the SW node to drive to ground naturally, this MOSFET forces the SW node toward ground and allow the bootstrap capacitor to charge.

Because this is a charge transfer circuit, care must be taken in selecting the value of the bootstrap capacitor. It must be sized such that the energy stored in the capacitor on a per cycle basis is greater than the gate charge requirement of the MOSFET being used.

#### **DESIGN HINT**

For the bootstrap capacitor, use a ceramic capacitor with a value between 22 nF and 82 nF.

#### NOTE:

For 5-V input applications, connect PVDDx to BP directly. This connection bypasses the internal control circuit regulator and provides maximum voltage to the gate drive circuitry. In this configuration, shutdown mode  $IDD_{SDN}$  will be the same as quiescent  $IDD_{O}$ .

## **Light Load Operation**

There is no special circuitry for pulse skipping at light loads. The normal characteristic of a nonsynchronous converter is to operate in the *discontinuous conduction mode* (DCM) at an average load current less than one-half of the inductor peak-to-peak ripple current. Note that the amplitude of the ripple current is a function of input voltage, output voltage, inductor value, and operating frequency, as shown in Equation 14.

$$I_{DCM} = \frac{1}{2} \times \frac{V_{IN} - V_{OUT}}{L} \times \delta \times T_{S}$$

(14)

Further, during discontinuous mode operation the commanded pulse width may become narrower than the capability of the converter to resolve. To maintain the output voltage within regulation, skipping switching pulses at light load conditions is a natural by-product of that mode. This condition may occur if the output capacitor is charged to a value greater than the output regulation voltage, and there is insufficient load to discharge the capacitor. A by-product of pulse skipping is an increase in the peak-to-peak output ripple voltage.

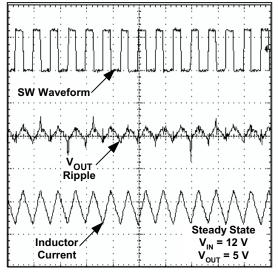

Figure 32. Steady State

Figure 33. Skipping

#### **DESIGN HINT**

If additional output capacitance is required to reduce the output voltage ripple during DCM operation, be sure to recheck *Feedback Loop and Inductor-Capacitor (L-C) Filter Selection* and *Maximum Output Capacitance* sections.

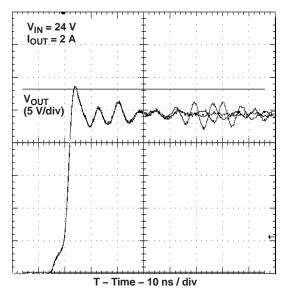

## **SW Node Ringing**

A portion of the control circuitry is referenced to the SW node. To ensure jitter-free operation, it is necessary to decrease the voltage waveform ringing at the SW node to less than 5 volts peak and of a duration of less than 30-ns. In addition to following good printed circuit board (PCB) layout practices, there are a couple of design techniques for reducing ringing and noise.

#### SW Node Snubber

Voltage ringing observable at the SW node is caused by fast switching edges and parasitic inductance and capacitance. If the ringing results in excessive voltage on the SW node, or erratic operation of the converter, an R-C snubber may be used to dampen the ringing and ensure proper operation over the full load range.

#### **DESIGN HINT**

A series-connected R-C snubber (C = between 330 pF and 1 nF, R = 10  $\Omega$ ) connected from SW to GND reduces the ringing on the SW node.

#### **Bootstrap Resistor**

A small resistor in series with the bootstrap capacitor reduces the turn-on time of the internal MOSFET, thereby reducing the rising edge ringing of the SW node.

#### **DESIGN HINT**

A resistor with a value between  $1\Omega$  and  $3\Omega$  may be placed in series with the bootstrap capacitor to reduce ringing on the SW node.

#### **DESIGN HINT**

Placeholders for these components should be placed on the initial prototype PCBs in case they are needed.

#### **Output Overload Protection**

In the event of an overcurrent during soft start on either output (such as starting into an output short), pulse-by-pulse current limiting and PWM frequency division are in effect for that output until the internal soft start timer ends. At the end of the soft start time, a UV condition is declared and a fault is declared. During this fault condition, both PWM outputs are disabled and the small pulldown MOSFETs (from SWx to GND) are turned ON. This process ensures that both outputs discharge to GND in the event that overcurrent is on one output while the other is not loaded. The converter then enters a *hiccup* mode timeout before attempting to restart. "Frequency Division" means if an overcurrent pulse is detected, six clock cycles are skipped before a next PWM pulse is initiated, effectively dividing the operating frequency by six and preventing excessive current build up in the inductor.

In the event of an overcurrent on either output after the output reaches regulation, pulse-by-pulse current limit is in effect for that output. In addition, an output undervoltage (UV) comparator monitors the FBx voltage (that follows the output voltage) to declare a fault if the output drops below 85% of regulation. During this fault condition, both PWM outputs are disabled and the small pulldown MOSFETs (from SWx to GND) are turned ON. This design ensures that both outputs discharge to GND, in the event that overcurrent is on one output while the other is not loaded. The converter then enters a *hiccup* mode timeout before attempting to restart.

The overcurrent threshold for Output 1 is set nominally at 4.5 A. The overcurrent level of Output 2 is determined by the state of the ILIM2 pin. The ILIM setting of Output 2 is not latched in place and may be changed during operation of the converter.

Table 2. Current Limit Threshold Adjustment for Output 2

| ILIM2 Connection | OCP Threshold for Output 2 |

|------------------|----------------------------|

| BP               | 4.5 A nominal setting      |

| (floating)       | 3.0 A nominal setting      |

| GND              | 1.5 A nominal setting      |

#### **DESIGN HINT**

The OCP threshold refers to the peak current in the internal switch. Be sure to add one-half of the peak inductor ripple current to the dc load current in determining how close the actual operating point is to the OCP threshold

## **Operating Near Maximum Duty Cycle**

If the TPS5438x operates at maximum duty cycle, and if the input voltage is insufficient to support the output voltage (at full load or during a load current transient), then there is a possibility that the output voltage will fall from regulation and trip the output UV comparator. If this should occur, the TPS5438x protection circuitry will declare a fault and enter a shut down-and-restart cycle.

#### **DESIGN HINT**

Ensure that under ALL conditions of line and load regulation, there is sufficient duty cycle to maintain output voltage regulation.

To calculate the operating duty cycle, use Equation 15.

$$\delta = \frac{V_{OUT} + V_{DIODE}}{V_{IN} + V_{DIODE}}$$

(15)

where

• V<sub>DIODE</sub> is the voltage drop of the rectifier diode

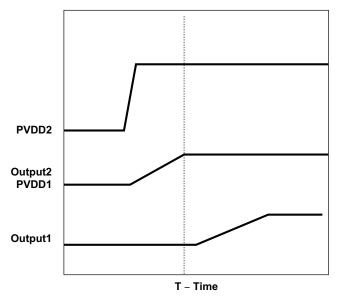

### **Dual Supply Operation**

It is possible to operate a TPS5438x from two supply voltages. If this application is desired, then the sequencing of the supplies must be such that PVDD2 is above the UVLO voltage before PVDD1 begins to rise. This level requirement ensures that the internal regulator and the control circuitry are in operation before PVDD1 supplies energy to the output. In addition, Output 1 must be held in the disabled state (EN1 high) until there is sufficient voltage on PVDD1 to support Output 1 in regulation. (See the *Operating Near Maximum Duty Cycle* section.)

The preferred sequence of events is:

- 1. PVDD2 rises above the input UVLO voltage

- 2. PVDD1 rises with Output 1 disabled until PVDD1 rises above level to support Output 1 regulation. With these two conditions satisfied, there is no restriction on PVDD2 to be greater than, or less than PVDD1.

#### **DESIGN HINT**

An R-C delay on EN1 may be used to delay the startup of Output1 for a long enough period of time to ensure that PVDD1 can support Output 1 load.

# **Cascading Supply Operation**

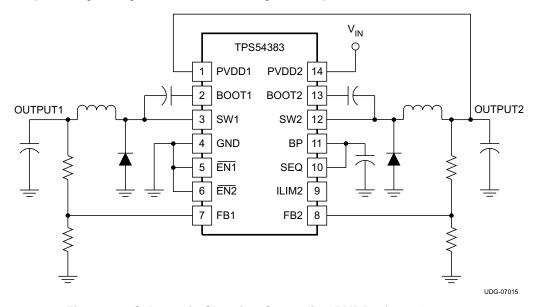

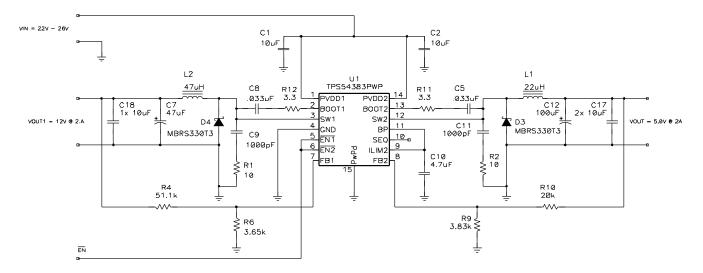

It is possible to source PVDD1 from Output 2 as depicted in Figure 34 and Figure 35. This configuration may be preferred if the input voltage is high, relative to the voltage on Output 1.

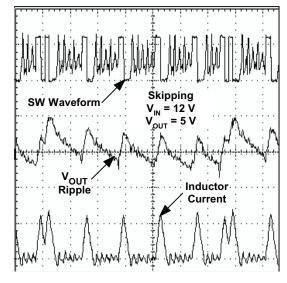

Figure 34. Schematic Showing Cascading PVDD1 from Output 2

Figure 35. Waveforms Resulting from Cascading PVDD1 from Output 2

In this configuration, the following conditions must be maintained:

- 1. Output 2 must be of a voltage high enough to maintain regulation of Output 1 under all load conditions.

- 2. The sum of the current drawn by Output 2 load plus the current into PVDD1 must be less than the overload protection current level of Output 2.

- 3. The method of output sequencing must be such that the voltage on Output 2 is sufficient to support Output 1 before Output 1 is enabled. This requrement may be accomplished by:

- a. a delay of the enable function

- b. selecting sequential sequencing of Output 1 starting after Output 2 is in regulation

#### **Multiphase Operation**

The TPS5438x is not designed to operate as a two-channel multiphase converter. See <a href="http://www.power.ti.com">http://www.power.ti.com</a> for appropriate device selection.

#### **Bypass and Filtering**

As with any integrated circuit, supply bypassing is important for jitter-free operation. To improve the noise immunity of the converter, ceramic bypass capacitors must be placed as close to the package as possible.

- 1. PVDD1 to GND: Use a 10-μF ceramic capacitor

- 2. PVDD2 to GND: Use a 10-uF ceramic capacitor

- 3. BP to GND: Use a 4.7-μF to 10-μF ceramic capacitor

## **Over-Temperature Protection and Junction Temperature Rise**

The over-temperature thermal protection limits the maximum power to be dissipated at a given operating ambient temperature. In other words, at a given device power dissipation, the maximum ambient operating temperature is limited by the maximum allowable junction operating temperature. The device junction temperature is a function of power dissipation, and the thermal impedance from the junction to the ambient. If the internal die temperature should reach the thermal shutdown level, the TPS5438x shuts off both PWMs and remains in this state until the die temperature drops below the hysteresis value, at which time the device restarts.

The first step to determine the device junction temperature is to calculate the power dissipation. The power dissipation is dominated by the two switching MOSFETs and the BP internal regulator. The power dissipated by each MOSFET is composed of conduction losses and output (switching) losses incurred while driving the external rectifier diode. To find the conduction loss, first find the RMS current through the upper switch MOSFET.

$$I_{RMS(outputx)} = \sqrt{D \times \left( \left( I_{OUTPUTx} \right)^2 + \left( \frac{\left( \Delta I_{OUTPUTx} \right)^2}{12} \right) \right)}$$

(16)

where

- D is the duty cycle

- I<sub>OUTPUTx</sub> is the dc output current

- ΔI<sub>OUTPUTx</sub> is the peak ripple current in the inductor for Outputx

Notice the impact of the operating duty cycle on the result.

Multiplying the result by the R<sub>DS(on)</sub> of the MOSFET gives the conduction loss.

$$P_{D(cond)} = I_{RMS(outputx)}^{2} \times R_{DS(on)}$$

(17)

The switching loss is approximated by:

$$P_{D(SW)} = \left[\frac{\left(V_{IN}\right)^2 \times C_J \times f_S}{2}\right] \tag{18}$$

where

- where C<sub>J</sub> is the prallel capacitance of the rectifier diode and snubber (if any)

- f<sub>S</sub> is the switching frequency

The total power dissipation is found by summing the power loss for both MOSFETs plus the loss in the internal regulator.

$$P_{D} = P_{D(cond)output1} + P_{D(SW)output1} + P_{D(cond)output2} + P_{D(SW)output2} + V_{IN} \times Iq$$

(19)

The temperature rise of the device junction depends on the thermal impedance from junction to the mounting pad (See the *Package Dissipation Ratings* table), plus the thermal impedance from the thermal pad to ambient. The thermal impedance from the thermal pad to ambient depends on the PCB layout (PowerPAD interface to the PCB, the exposed pad area) and airflow (if any). See the *PCB Layout Guidelines, Additional References* section.

The operating junction temperature is shown in Equation 20.

$$T_{J} = T_{A} + P_{D} \times \left(\theta_{TH(pkg)} + \theta_{TH(pad-amb)}\right)$$

(20)

#### **Power Derating**

The TPS5438x delivers full current at ambient temperatures up to +85°C if the thermal impedance from the thermal pad maintains the junction temperature below the thermal shutdown level. At higher ambient temperatures, the device power dissipation must be reduced to maintain the junction temperature at or below the thermal shutdown level. Figure 36 illustrates the power derating for elevated ambient temperature under various airflow conditions. Note that these curves assume that the PowerPAD is properly soldered to the recommended thermal pad. (See the *References* section for further information.)

Figure 36. Power Derating Curves

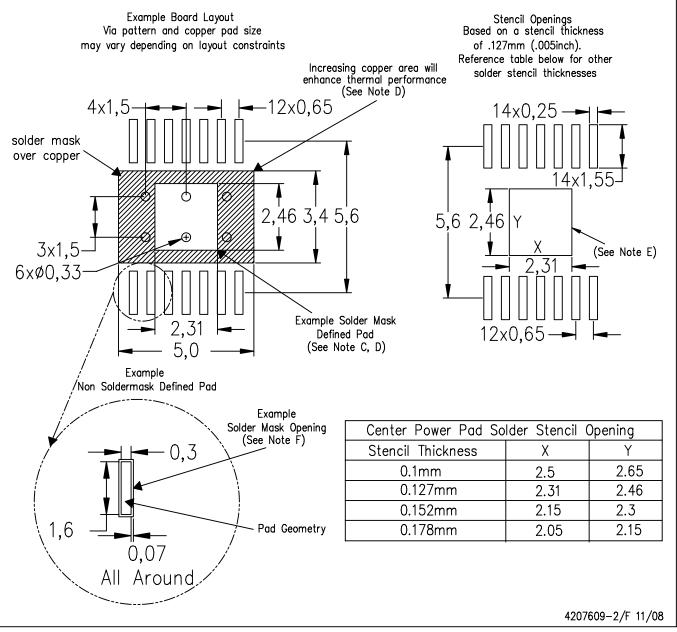

#### PowerPAD Package

The PowerPAD package provides low thermal impedance for heat removal from the device. The PowerPAD derives its name and low thermal impedance from the large bonding pad on the bottom of the device. The circuit board must have an area of solder-tinned-copper underneath the package. The dimensions of this area depend on the size of the PowerPAD package. Thermal vias connect this area to internal or external copper planes and should have a drill diameter sufficiently small so that the via hole is effectively plugged when the barrel of the via is plated with copper. This plug is needed to prevent wicking the solder away from the interface between the package body and the solder-tinned area under the device during solder reflow. Drill diameters of 0.33 mm (13 mils) work well when 1-oz. copper is plated at the surface of the board while simultaneously plating the barrel of the via. If the thermal vias are not plugged when the copper plating is performed, then a solder mask material should be used to cap the vias with a diameter equal to the via diameter of 0.1 mm minimum. This capping prevents the solder from being wicked through the thermal vias and potentially creating a solder void under the package. (See the *Additional References* section.)

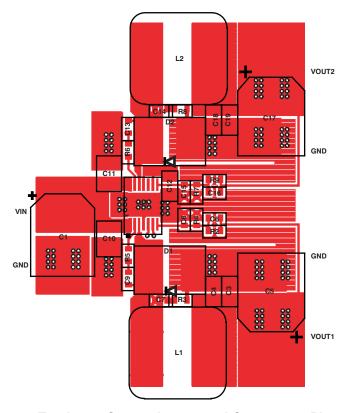

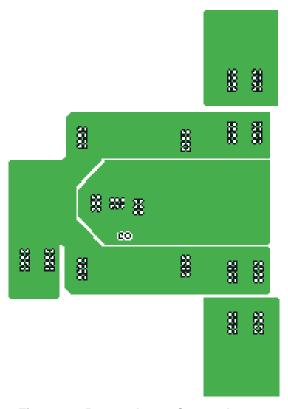

#### **PCB Layout Guidelines**

The layout guidelines presented here are illustrated in the PCB layout examples given in Figure 37 and Figure 38.

- The PowerPAD must be connected to a low current (signal) ground plane having a large copper surface area

to dissipate heat. Extend the copper surface well beyond the IC package area to maximize thermal transfer of

heat away from the IC.

- Connect the GND pin to the PowerPAD through a 10-mil (.010 in, or 0.0254 mm) wide trace.

- Place the ceramic input capacitors close to PVDD1 and PVDD2; connect using short, wide traces.

- Maintain a tight loop of wide traces from SW1 or SW2 through the switch node, inductor, output capacitor and rectifier diode. Avoid using vias in this loop.

- Use a wide ground connection from the input capacitor to the rectifier diode, placed as close to the power path as possible. Placement directly under the diode and the switch node is recommended.

- Locate the bootstrap capacitor close to the BOOT pin to minimize the gate drive loop.

- Locate voltage setting resistors and any feedback components over the ground plane and away from the switch node and the rectifier diode to input capacitor ground connection.

- Locate snubber components (if used) close to the rectifier diode with minimal loop area.

- Locate the BP bypass capacitor very close to the IC; a minimal loop area is recommended.

- Locate the output ceramic capacitor close to the inductor output terminal between the inductor and any electrolytic capacitors, if used.

Figure 37. Top Layer Copper Layout and Component Placement

Figure 38. Bottom Layer Copper Layout

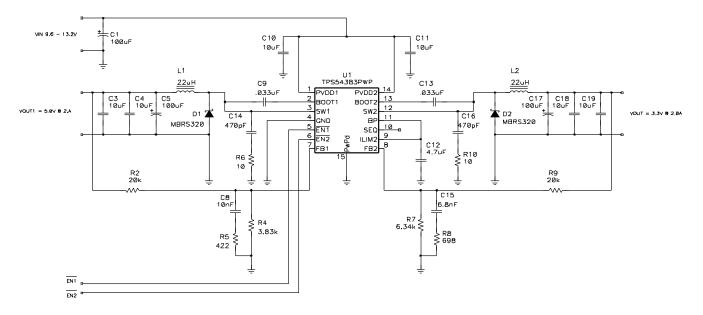

## **DESIGN EXAMPLES**

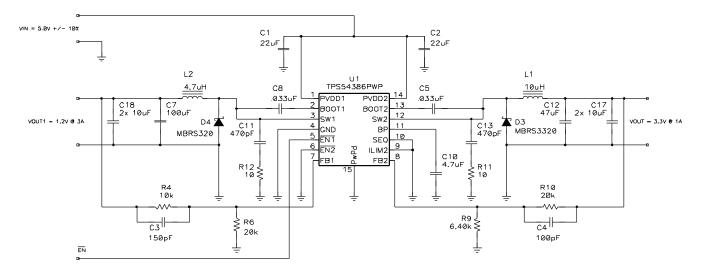

# Example 1: Detailed Design of a 12-V to 5-V and 3.3-V Converter

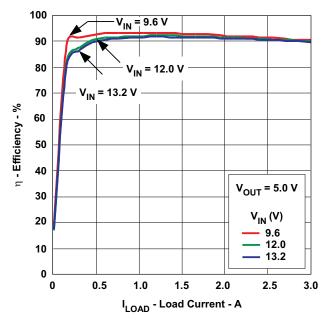

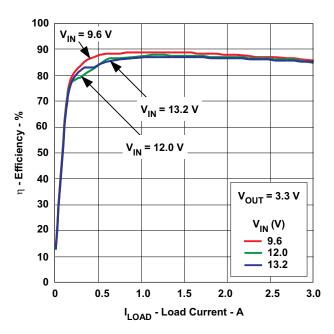

The following example illustrates a design process and component selection for a 12-V to 5-V and 3.3-V dual non-synchronous buck regulator using the TPS54383 converter. Design Example List of Materials and Table 4, Definition of Symbols is found at the end of this section.

| PARAME                    | TER                                                      | NOTES AND CONDITIONS                                             | MIN | NOM  | MAX  | UNIT      |

|---------------------------|----------------------------------------------------------|------------------------------------------------------------------|-----|------|------|-----------|

| INPUT CH                  | HARACTERISTICS                                           |                                                                  | -   |      |      | •         |

| V <sub>IN</sub>           | Input voltage                                            |                                                                  | 6.9 | 12.0 | 13.2 | V         |

| I <sub>IN</sub>           | Input current                                            | V <sub>IN</sub> = nom, I <sub>OUT</sub> = max                    |     | 1.6  | 2.0  | Α         |

|                           | No load input current                                    | V <sub>IN</sub> = nom, I <sub>OUT</sub> = 0 A                    |     | 12   | 20   | mA        |

| OUTPUT                    | CHARACTERISTICS                                          |                                                                  | ·   |      |      |           |

| V <sub>OUT1</sub>         | Output voltage 1                                         | V <sub>IN</sub> = nom, I <sub>OUT</sub> = nom                    | 4.8 | 5.0  | 5.2  | V         |

| V <sub>OUT2</sub>         | Output voltage 2                                         | V <sub>IN</sub> = nom, I <sub>OUT</sub> = nom                    | 3.2 | 3.3  | 3.4  |           |

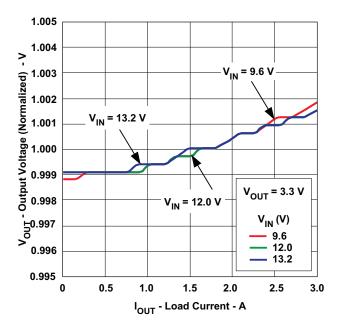

|                           | Line regulation                                          | V <sub>IN</sub> = min to max                                     |     |      | 1%   |           |

|                           | Load regulation                                          | I <sub>OUT</sub> = min to max                                    |     |      | 1%   |           |

| V <sub>OUT(ripple</sub> ) | Output voltage ripple                                    | V <sub>IN</sub> = nom, I <sub>OUT</sub> = max                    |     |      | 50   | $mV_{PP}$ |

| I <sub>OUT1</sub>         | Output current 1                                         | V <sub>IN</sub> = min to max                                     | 0   |      | 2.0  | A         |

| I <sub>OUT2</sub>         | Output current 2                                         | V <sub>IN</sub> = min to max                                     | 0   |      | 2.0  |           |

| I <sub>OCP1</sub>         | Output overcurrent channel 1                             | V <sub>IN</sub> = nom, V <sub>OUT</sub> = V <sub>OUT1</sub> = 5% | 2.4 | 3    | 3.5  |           |

| I <sub>OCP2</sub>         | Output overcurrent channel 2                             | V <sub>IN</sub> = nom, V <sub>OUT</sub> = V <sub>OUT2</sub> = 5% | 2.4 | 3    | 3.5  |           |